|

|

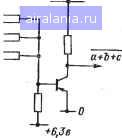

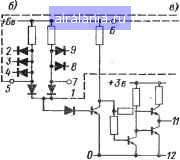

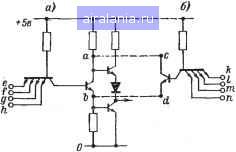

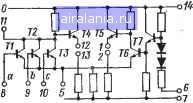

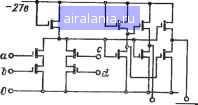

Главная -> Современная электроника 0 1 2 3 4 [5] 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 в ИС серии К217 ( + 3 в и +6 в) вызвано стремлением увеличить быстродействие и уменьшить потребляемую мощность ИС [22]. Если коллекторы транзисторов двух ТЛЭ, входящих в ИС К2ЛБ172 (выводы 2 и ), соединить между собой, а напряжение питания -f3 в подать только на один ТЛЭ (иа вывод / или на вывод 10), то получим схему, реализующую функцию «И-ИЛИ-НЕ». Если обозначить входные сигналы схемы буквами л: с индексами, соответствующими номерам выводов ИС (см. рис. 6, а), то на выходе в этом случае получим функцию -Б.Зе  р2. 11 - XgXXc, + XXgXi,. Принципиальная схема ИС К2ЛР171 (рис. 6,6) иллюстрирует ; ругой метод построения схемы «И-ИЛИ-НЕ». В отличие от схемы, показанной на рис. 6, а, в схеме К2ЛР171 не только функция «И», но и функция «ИЛИ» выполняется с помощью диодов. Благодаря наличию вспомогательных выводов в схеме К2ЛР171 возможно увеличение числа входов схем «И» и «ИЛИ». Для этого используется расширитель К2ЛП173 (рис. 6, в). Если, например, присоединить выводы 5, 12, 8 схемы К2ЛП173 к выводам соответственно /, 6, 5 схемы К2ЛР171 (рис. 5), то получим схему «И-ИЛИ-НЕ», реализующую функцию Рис. 5. Схема типового логического элемента ИС серии К210 = Х2ХзХУеУ.,УдУ10 + XgXs + У1У2Уа . где л: -входные сигналы ИС К2ЛР171 и / -входные сигналы ИС К2ЛП171. Сравнивая схемы рис. 6, а и 6, б, можно увидеть два варианта построения транзисторных инверторов. Инверторы, входящие в ИС К2ЛБ172, со- 1 10 Jo-M- И И +6в I об V О -*-о  1Щ IfW-e 2-К I W-7 Рис. 6. Схема ИС типов К2ЛБ172 (а), К2ЛР171 (б) и К2ЛП173 (е) стоят из одного транзистора, в то время как инвертор в ИС К2ЛР171 содержит четыре транзистора и обеспечивает повышенную нагрузочную способность. Транзисторно-транзисторные логические схемы (ТТЛ) состоят из цепи «И», построенной на основе многоэмиттерного транзистора, и транзисторного инвертора. На рис. 7, а показана принципиальная схема четырехвходового типового логического элемента транзисторно-транзисторной серии К155. Многоэмиттер-ный транзистор в схеме 7, а образует четырехвходовую цепь «И». В случае присоединения хотя бы одного эмиттера этого транзистора к потенциалу.  Рис. 7. элемента Схема типового логического (а) и логического расширителя (б) ИС серии К155 близкому к нулю, транзистор насыщается и тем самым присоединяет к нулевому потенциалу вход инвертора, состоящего из трех одноэмиттерных транзисторов. Если же на все входы (эмиттеры) цепи «И» подан потенциал, близкий к напряжению питания (потенциал «1»), то база-коллекторный переход многоэмиттерного транзистора оказывается смещенным в прямом направлении. Этот переход открывается, и ток из базовой цепи транзистора поступает на вход инвертора. Дополнительные выводы от точек а и b инвертора (рис. 7, а) позволяют реализовать схему «И-ИЛИ-НЕ» путем присоединения к этим точкам выводов с и d логического расширителя (рис. 7,6). В состав серии К155 входят также готовые схемы «И-ИЛИ- НЕ» (например, К1ЛР551). Схемы серии К155 выпускаются в пластмассовом корпусе (см. рис. 3, е). Транзисторные логические схемы на переключателях тока (ПТТЛ) отличаются от рассмотренных выше схем ИС тем, что открытые транзисторы в них не входят в режим насыщения. Благодаря этому повышается быстродействие таких схем l3, 22]. На основе переключателей тока построена серия логических ИС 137. На рис. 8 показана принципиальная схема ИС 1ЛБ371. Схема содержит четыре эмиттерно-связанных каскада (транзисторы Г/, Т2, ТЗ, Т6), два эмиттерных повторителя (транзисторы Т4 и Т5) и источник опорного напряжения (транзистор Т7). Для рассмотрения работы схемы предположим, что между собой соответственно соединены выводы 12 и 13, 1 и 2, 6 и 7. Если на входы 8, 9 а 10 поданы потенциалы, соответствующие уровню «О»,, то транзисторы Т1, Т2, ТЗ закрыты, транзистор же Т6 открыт, так как на его вход подано опорное напряжение, с эмиттера транзистора Т7, превышающее уровень «О». Но если хотя бы на один из входов 8, 9 или 10 подать напряжение, соответствующее уровню «1» (большее по величине, чем опорное напряжение, снимаемое с эмиттера транзистора Т7), то соответствующий транзистор Т1, Т2 или ТЗ откроется (но не войдет в режим насыщения), а транзистор Т6 закроется. Таким образом, напряжение на выходе эмиттерного повторителя на транзисторе Г4-близко к напряжению питания (соответствует уровню «1») тогда, когда на всех входах схемы присутствует потенциал, соответствующий уровню «О». Если же хотя бы на одном входе потенциал соответствует единице, то на выходе этого повторителя получаем низкий уровень, соответствующий нулю. Следовательно, сигнал с выхода повторителя на транзисторе Т4 соответствует функции «НЕ-ИЛИ» от трех входных сигналов. Поскольку транзистор Т6 закрыт тогда, когда открыт один из транзисторов Т1, Т2 или ТЗ, то с выходов эмиттерного повторителя на транзисторе То снимаем сигнал, который равен инверсии сигнала с триода Т4, т. е. сигнал, соответствующий функции «ИЛИ» от трех входных сигналов.  Рис. 8. Схема ИС типа 1ЛБ371  аЪ+cd аЪ+cd Рис. 9. Схема «И-ИЛИ-НЕ» (И-ИЛИ) на МОП-транзисторах Перепады выходных напряжений, снимаемых со схем ПТТЛ, не превышают падений напряжения на открытом переходе база - эмиттер транзистора (0,7-0,9 в). Эмиттеры транзистора Т4 и Т5 не соединены внутри ИС со своими эмит-терными резисторами, что дает возможность присоединять выходы нескольких схем к одному эмиттерному резистору. Тем самым будет образована схема «ИЛИ» для выходных сигналов нескольких ИС. Увеличение входов ИС 1ЛБ371 может быть произведено путем присоединения к выводам 5 н и дополнительных транзисторов, содержащихся в расширителе 1ЛП371. При рассмотрении схемы рис. 8 мы все входные и выходные напряжения отсчитывали от отрицательной шины источника питания. Однако следует заметить, что в схемах ПТТЛ обычно заземляют положительную (коллекторную) шину источника питания. В этом случае все входные и выходные напряжения таких ИС имеют отрицательный знак. Если при этом считать уровнями «1» и «О» соответственно высокий и низкий отрицательные потенциалы относительно заземленной шины источника питания, то окажется, что схемы ПТТЛ выполняют функции «НЕ - И» и «И». Заземление положительной, а не отрицательной шины источника питания в схемах ПТТЛ приводит к более высокому отношению уровня «1» к уровню «О» (абсолютный перепад напряжения при этом, естественно, остается тем же самым). Логические схемы на основе транзисторов типа МОП (МОПТЛ) могут содержать как схемы «НЕ-И», так и схемы «НЕ-ИЛИ», а также схемы «И», «И-ИЛИ-НЕ» и т. д. На рис. 9 показана схема «И-ИЛИ-НЕ», входящая в ИС К1ЛР172. Схемы «И» и «ИЛИ» в данном случае образуются путем последовательного и параллельного включения МОП-транзисторов. В отличие от схем на биполярных транзисторах в схемах МОПТЛ в качестве нагрузочных резисторов используются открытые МОП-транзисторы. Благодаря этому упрощается технология изготовления ИС и, кроме того, увеличивается плотность размещения, так как МОП-транзистор занимает на подложке меньшую площадь, чем диффузионный резистор. В логических схемах на МОП-транзисторах отсутствуют элементы (резисторы, диоды) в цепи связи между выходом одного транзистора и входом другого. Это объясняется высоким входным сопротивлением МОП-транзисторов, которое определяется практически только утечками в изоляции и достигает величины 102-" ом. Как правило, в схемах МОПТЛ используются МОП-транзисторы, работающие в режиме обогащения, с каналом р-типа. Для того чтобы открыть такой транзистор, ему на затвор нужно подать достаточно большое отрицательное напряжение. Очень высокое входное сопротивление МОП-транзисторов, являясь несомненно их преимуществом, вместе с тем вызывает ряд трудностей при работе с ними. Напряжение пробоя изоляционного слоя окисла между затвором и каналом обычно лежит в диапазоне 30-50 в. Если на затвор МОП-транзистора попадает более высокое напряжение, то происходит пробой изоляции и транзистор выходит из строя. Поскольку сопротивление затвор - канал может достигать, как было указано, 10*-10" ом, то даже если источник напряжения отделен от затвора МОП-транзистора изоляцией с сопротивлением 10-10*" ом, практически все напряжение источника будет приложено к затвору. 0 1 2 3 4 [5] 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 0.0082 |